Impedance describes the total measure of opposition to electrical current flow within a circuit. Managing impedance proves vital for avoiding unintended resistance that degrades signals transferred across traces in high-frequency printed circuit board (PCB) designs.

By mathematically modeling a PCB stackup configuration, engineers determine expected impedance values for board layouts during the design stage itself, before prototyping. This allows optimizing circuit parameters targeting the desired impedance early when changes cost less.

We will explore what constitutes impedance, why control matters for certain traces, available calculators, how to model a PCB stackup, select suitable dielectrics, and derive impedance equations – demystifying the analysis process.

The Basics of Impedance

Impedance generalizes resistance, inductance and capacitance into a single unified quantity summarizing total opposition to current or voltage in an alternating current (AC) circuit. Since PCBs carry high-frequency signals, managing impedance grows necessary.

Resistance

Resistance (R) arises from collisions of current flow against material like copper. It converts electrical energy into heat, incurring loss.

Inductance

Changes in current generate a magnetic field Manifesting as self-induced voltage. Inductance (L) quantifies this field strength opposing variations in current.

Capacitance

Capacitance (C) represents how charge separates between conductors across an insulator. This stores electric fields, resisting voltage changes.

Impedance

By unifying R + L + 1/C (capacitive reactance) into a single impedance (Z) value, we simplify the overall opposition acting on signals. Controlling impedance through intentional PCB design prevents unintended resistance.

Why Control Impedance?

For low speed circuits impedance matters less – traces simply need to conduct safely. But in high frequency applications:

Signal Integrity

Controlled impedance traces minimize reflections and electromagnetic interference that corrupt signals and limit edge rates.

Power Integrity

Steady characteristic impedance allows termination schemes managing resonances/ringing on power rails thatCouples noise into circuits.

High Speed Communications

Maintaining target differential impedance supports precise transmission line behavior for multi-Gbps serialized IOs including PCIe, Ethernet, USB.

In these cases, modeling impedance during layout enables optimizing PCB stackups accordingly. Otherwise signal quality and system reliability suffer once manufactured.

Analyzing Impedance

Since impedance links strongly to layout construction and materials, accurate modeling before prototyping lets engineers assess performance of traces based on width, spacing and dielectric constants according to frequency needs of signals.

Analysis determines expected impedance (Z0) for board configurations using closed form equations applied to geometry and material properties. Evaluation requires detailing:

- Conductor thickness/width

- Spacing to reference planes

- Dielectric constant (Dk) and loss tangent for all insulating materials

- Target frequency range

Using these design properties in calculations predicts impedance looking into traces to match interface requirements. If impedance mismatches above tolerances, alterations to stackup resolve this before tapeout.

Modeling the PCB Stackup

Before applying impedance formulas, engineers construct an accurate model capturing the layer-by-layer PCB stackup. Details like:

- Number of conductive layers (2 to 30+)

- Copper weight (1oz/ft2 standard; 2oz+ typical for high frequency)

- Core thickness (60mil to 240mil)

- Prepreg type and thickness around cores

- Dielectric constants per material

- Locations of signal vias/antipads

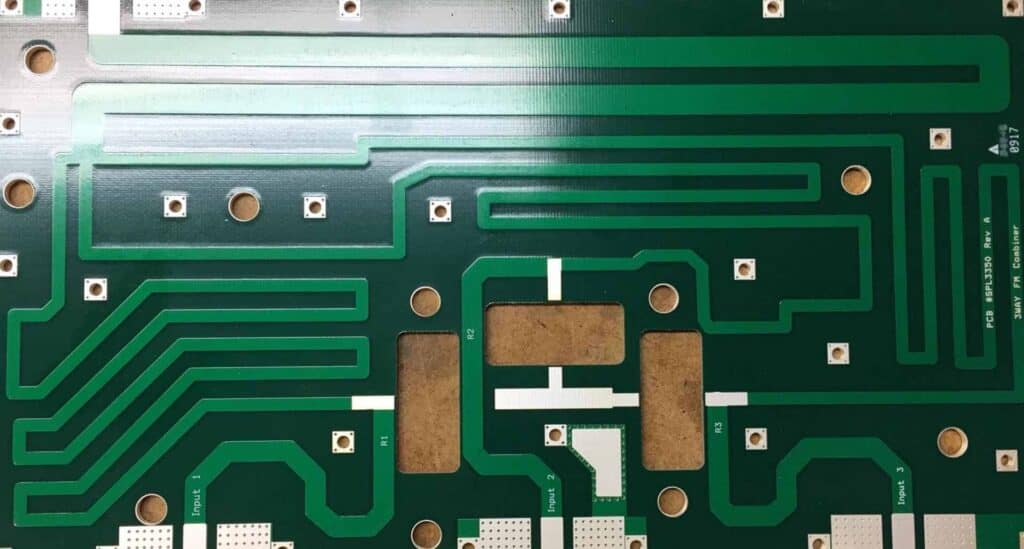

SEM cross-sections aid modeling intricate constructions:Copy code

[Picture of SEM Cross-section]

With an accurate stackup reference, the dielectric environment surrounding critical signal traces becomes clear. The materials adjacent traces route through along their path length determines impedance.

Dielectric Performance Considerations

The type of insulating dielectric materials utilized impacts impedance. Key electrical properties include:

| Dielectric Property | Description |

|---|---|

| Dielectric Constant (Dk) | Permittivity influencing impedance and propagation velocity |

| Loss Tangent (Df) | Signal lossiness – higher values absorb more energy |

| Moisture Absorption | Water uptake degrades electrical performance |

| Z-Axis CTE | Out-of-plane thermal expansion affects reliability |

| Glass Transition (Tg) | Temperature where material softens losing rigidity |

Generally, materials with Dk under 5 and loss tangents below 0.02 support best high frequency signal integrity. But this balances against cost, processability and mechanical needs influencing material selection.

Stackup Construction Approaches

Optimizing impedance requires strategic stackup design and laminate choices fitting frequency ranges of signals in play. Common configurations include:

| Construction | Description | Benefits |

|---|---|---|

| Microstrip | Signal conductors with ground plane below | Simple to model impedance only depends on trace dimensions and height above ground |

| Stripline | Signals between two reference planes | Superior noise isolation with consistent surroundings enabling tightly controlled impedance |

| Differential Pairs | Two coupled traces linking I/O | Twisted geometry with controlled differential impedance minimizes EMI while retaining signal fidelity |

| Buried Cores | Reference planes embedded internally | Removes unused layers separating traces from nearest ground lowering impedance |

| Impedance-Tailored Dielectrics | Alternating prepreg types | Localized high/low Dk zones fine tune impedance |

Reviewing various stackup arrangements determines which helps dial in target impedance most precision given cost and complexity tradeoffs acceptable for an application.

Quick Estimates using Online Calculators

Before diving into comprehensive analysis, free online tools like Saturn PCB’s Impedance Calculator rapidly estimate transmission line impedance. Simply enter:

- Dielectric height

- Conductor width

- Dielectric constant

And the calculator outputs an approximate impedance value for the microstrip structure. The Saturn Toolkit even estimates line inductance and capacitive load limits.

These handy reference calculators generate reasonable ballpark Z0 targets for quick sanity checks during layout when precision results are not yet vital.

Applying Closed Form Equations

To accurately determine expected impedances for key traces based on exact dielectric constants and desired geometries, mathematical equations codify the precise physics linking materials and construction to electrical behavior.

Closed form formulas make assumptions constraining their accuracy range, but solve straightforwardly. Two common approaches include:

Schneider Equations

Schneider approximations model microstrip impedance representing typical PCB routing covering a ground plane:Copy code

Z0 = 60/√εr * ln[(5.98h)/(0.8w + t)]

Where:

- εr = dielectric constant

- h = dielectric thickness

- w = trace width

- t = trace thickness

The equation simplifies modeling surface traces separated from an immediate reference plane. More advanced Schneider formulations improve accuracy for very thick dielectrics.

Conformal Mapping Equations

For stripline arrangements where symmetrically sandwiching reference planes enclose signals, conformal mapping equations like Hammerstad apply:Copy code

Z0 = (87/( εr + 1.41)) * ln((5.98h)/(0.8w + t))

The double-sided plane symmetry makes this equation well-suited for modeling differential pair and internal signal routing constructions.

Plugging values into these foundational formulas generates reliable impedance estimations for anticipated stackups to guide early design rules.

Modeling Differential Pairs

Prolific modern uses of high-speed differential signaling like USB and HDMI demand precision impedance calculations when laying out coupled differential pairs between ground planes.

Modeling considers effective dielectric constants, spacing, plane thickness, and trace dimensions targeting 100Ω differential impedance along with intra-pair consistencies.

Analysis may leverage closed forms equations or employ 3D field solvers for tightly coupled geometries beyond classic modeling limitations. Matching propagation velocities between positive and negative paths ensures synchronized arrival for reliable reception interpreting signals.

Careful correlated modeling guides properly routing, truncating and tuning dielectric properties when designing differential interfaces sensitive to impedance fluctuations degrading traffic quality.

De-embedding Surface Pad Capacitance

Accurate modeling must also account for extra capacitive load added to signals from surface mount pads sitting along the path separate from transmission line geometry modeled.

This pad capacitance often approaches ~0.5pF adding impedance deviations risking overshoot, ringing and noise injection since the pads form parasitic capacitors to ground.

Subtracting pad loading from overall modeled impedance keeps trace transmission models pure and helps determine appropriate line termination schemes so reflections stay managed.

Assessing Model Accuracy

To validate if modeled target impedances align sufficiently with real measured results, PCB metrology tests constructed boards. Comparison between prediction and measured values provides a pass/fail gauge before committing to volume fabrication if the design suits its intended functionality.

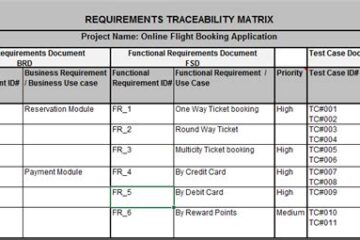

TDR Testing

Time domain reflectometry analysis injects a pulse propagating down traces. Based on load reflections, an oscilloscope-like waveform captures impedance discontinuities along the line indicating if trace construction gives expected impedance.

[Picture of a TDR test waveform plot]

Spikes or plateaus reveal inconsistencies from intended impedance. Smooth flat traces meeting target values validate solid modeling.

DC Resistance Testing

A simpler four-point DC resistance measurement between differential endpoints also validates construction by confirming resistance falls within a nominal ±10% window of the 100Ω expectation for differential signaling.

Out of spec measures require re-modeling stackups and rerouting traces before full manufacture. In spec values verify modeling accuracy.

Repeatable impedance-controlled routing requires correlating modeled performance to measured metrics across multiple test vehicles to instill modeling confidence covering all expected PCB stackup constructions.

Incorporating Results Back into Design Rules

Once modeling a few test cases reflects real performance, codifying learnings as constraints in layout rules ensures consistent impedance compliance:

- Specify target trace geometry ratios for target impedance

- Constrain dielectric selections around critical nets

- Define reference planes/clearances for microstrip Z0

- Control differential pair coupling gap/skew

- Load matching parameters for trace tuning

These rules bake modeled target values into the PCB layout environment for rapid application across designs, propagating impedance control fidelity.

Configuring Stackups for Target Impedance Goals

Armed with accurate modeling capabilities, we can methodically configure board stackup constructions targeting exact impedance ranges needed for signals based on data rates served.

Suppose we want to route 10Gbps ethernet (ideally 100Ω differential) but also need some single-ended 50Ω impedance interfaces:

Layer Planning

We allocate layer pairs to separate 10GbE differential pairs routing closely spaced between adjacent ground layers for controlled impedance up to 100Ω based on models. Wider spaced 50Ω single-ended traces route on outer layers.

Dielectric Selection

Prepregs get strategically inserted with low loss, tighter impedance weave 7628 material under the critical 10GbE traces while allowing standard FR-4 prepreg insulating other layers.

Final Layer Stackup

Copy code

Impedance-Optimized 10 Layer Construction ------------------------------------------------- L1: 50 Ohm Signaling FR4 Prepreg L2: Ground Plane L3: Differential Pair 1 - 100 Ohm Impedanced 7628 Prepreg L4: Ground Plane L5: Differential Pair 2 - 100 Ohm Impedanced 7628 Prepreg L6: Ground Plane L7: Plain FR4 Prepreg L8: Ground Plane L9: 50 Ohm Signaling FR4 Prepreg L10: Ground Plane

This arrangement applies precision dielectric selection with modeling-driven stackup arrangement to achieve targeted impedance performance.

Further Optimizing Impedance Control

Beyond fundamental stackup construction and layout rules, additional techniques refining impedance incorporation include:

Leverage Cross-sectional Analyses

Modeling formulas make simplifying assumptions. Full 3D field solvers modeling complex edge cases improve accuracy.

Tune Trace Widths adaptively

Control impedance through adaptive routing where trace widths narrow/widen responding to spacing changes from obstacles.

Limit Layer Transitions

Minimize drilling through multiple plane layers which affects impedance

Review Weave Impacts

Model glass weave undulations in prepregs influencing local impedance

Simulate Routing Detours

Analyze impedance changes from zig-zag escape patterns detouring around densely packed BGAs

While achieving target controlled impedance requires effort, the signal and power integrity payoffs outweigh increasing modeling intricacy necessary for today’s high-frequency PCBs.

Conclusion

This detailed overview exploring PCB impedance determination covered key points:

- Why impedance control matters for signal quality

- Details for modeling relevant PCB stackup attributes

- Analyzing impedance using free calculators or closed form equations

- Construction approaches balancing cost and performance

- Model validation through TDR testing and DC resistance measures

- Optimizing configurations targeting specific impedance goals

By learning methodologies assessing stackup impedance early in the design phase, engineers confidently design-in controlled transmission lines ensuring reliable function after assembling into products.

Going through disciplined modeling workflows pays dividends lowering field failures and costly reworks down the line once a validated strategy for construing impedance tailored PCBs proves consistent performance aligning intent to measured results.

Frequently Asked Questions

Here are answers to some common questions about calculating PCB impedance:

Do I need to perform impedance calculations if not using high speed interfaces?

Normal interconnect rates under 50MHz or so may not necessitate detailed modeling. Use good layout practices avoiding noisy spots. But adding supply decoupling never hurts!

How accurately do online calculators estimate results compared to graphically-solved formulas?

Simple calculators give decent estimates to narrow viable constructions, especially for initial scoping. But validated modeling equations applied against final stackups always serve best before finalizing fabrication.

Can I adjust a too-high impedance PCB simply by making traces wider?

Yes, increasing trace widths lowers impedance, but at some point spacing constraints intervene. Adjusting prepreg dielectric properties or reducing trace-to-plane clearances offer additional levers tailored to target values.

Where should I probe signals to best correlate TDR impedance measurements against modeled values?

Measure impedance along at multiple points along the path length, avoiding discontinuities like vias or component lands. Time domain waveforms visualize impedance dips clearly to diagnose issues.

Do manufacturers themselves ever assist modeling impedance for their specific material processes?

Absolutely. Many fabricators characterize various stackup recipes across their prepreg and laminates offerings and will recommend validated constructions pairing materials and modeling to achieve target results.

0 Comments